IPrium releases 40G I.3 Encoder/Decoder for DWDM systems

FOGGIA, Italy, December 27, 2016 - FPGA intellectual property (IP) provider IPrium LLC (www.iprium.com) has today announced that it has expanded its family of Super-FEC IP products with a new OTU3 40G I.3 BCH Codec IP Core for the G.975.1 standard.

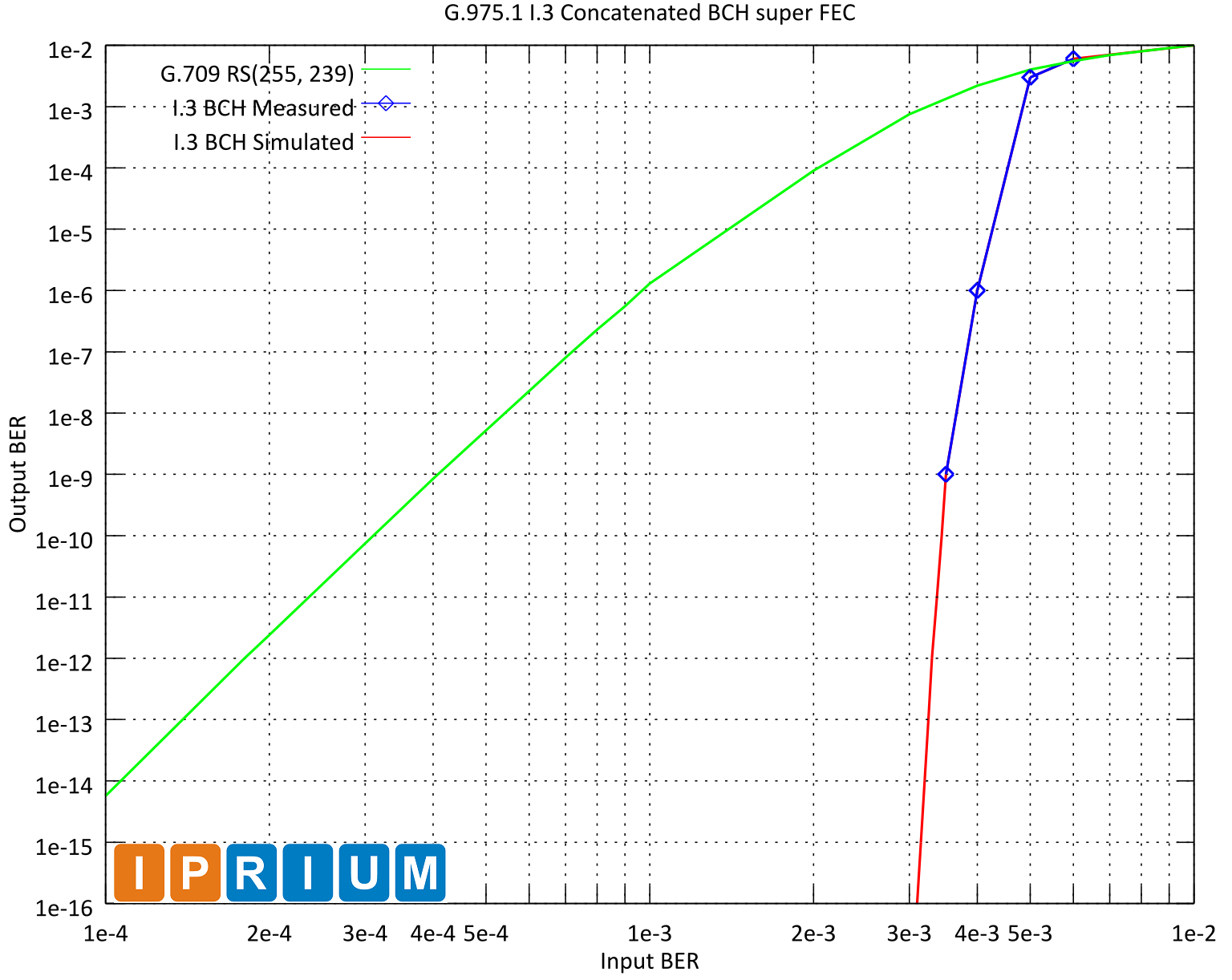

The IP Core is a complete Encoder and Decoder module, optimized for 40-46 Gbit/s optical communication systems. The redundancy ratio of the super-FEC code is 6.69% and the net coding gain is 9.26 dB for output BER=1e-16.

The 40G I.3 BCH Codec is silicon-proven and is fully compliant with ITU-T G.975.1 Standard (as of 02/2004) "Forward error correction for high bit-rate DWDM submarine systems. Appendix I. Super FEC schemes I.3 Concatenated BCH super FEC code".

The IP Core provides a turnkey single-chip solution that can be used in low-cost high-throughput applications.

Pricing and Availability

The 40G I.3 BCH Codec IP Core is available immediately in synthesizable Verilog or optimized netlist format, along with synthesis scripts and a simulation test bench with expected results.

For further information, a product evaluation or pricing, please visit the IP Core page:

About IPrium LLC

IPrium Modem IP Cores allow designers of communication equipment to rapidly develop and verify their systems in a highly cost-effective manner. IPrium offers FPGA IP Cores for high-quality wireless and wireline modems. Visit IPrium at www.iprium.com.

return